# **Logic Gates**

Logic gates take four pairs of inputs: 10, 01, 11 and 00 and for each pair generate an output. There are six logic gates, which form into pairs affording mirror opposite outputs. The order in which the input pairs are considered does not change the logic gate.

| Input 1 |   | X | OR |   |

|---------|---|---|----|---|

|         | 1 | 0 | 1  | 0 |

| Input 2 | 0 | 1 | 1  | 0 |

| Output  | 1 | 1 | 0  | 0 |

|         |   | O | R |   |

|---------|---|---|---|---|

| Input 1 | 1 | 0 | 1 | 0 |

| Input 2 | 0 | 1 | 1 | 0 |

| Output  | 1 | 1 | 1 | 0 |

| Input 1 |   | Al | ND |   |

|---------|---|----|----|---|

|         | 1 | 0  | 1  | 0 |

| Input 2 | 0 | 1  | 1  | 0 |

| Output  | 0 | 0  | 1  | 0 |

|         | XNOR  |   |   |   |

|---------|-------|---|---|---|

| Input 1 | 1 0 1 | 0 |   |   |

| Input 2 | 0     | 1 | 1 | 0 |

| Output  | 0     | 0 | 1 | 1 |

| Input 1 |   | N | OR |   |

|---------|---|---|----|---|

|         | 1 | 0 | 1  | 0 |

| Input 2 | 0 | 1 | 1  | 0 |

| Output  | 0 | 0 | 0  | 1 |

|         |   | NA | ND |   |

|---------|---|----|----|---|

| Input 1 | 1 | 0  | 1  | 0 |

| Input 2 | 0 | 1  | 1  | 0 |

| Output  | 1 | 1  | 0  | 1 |

### **LOGIC GATES**

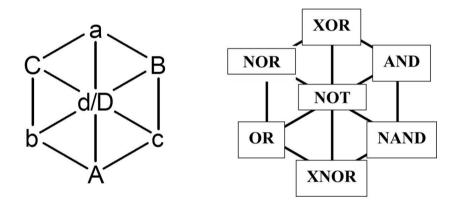

The six logic gates paired according to their mirror opposite outputs. The outputs appear to be independent of the order of the input pairs.

However there are six, not eight logic gates for a reason. The system is controlled by the symmetry of Order 4. The four different inputs 10, 01, 11 and 00 can only be ordered to generate meaning in six ways. Each logic gate in a mirror pair does not simply have opposite output symbols; it is the mirror opposite of its counterpart: each logic gate is not another.

|         |   | X | OR |   |

|---------|---|---|----|---|

| Input 1 | 1 | 0 | 1  | 0 |

| Input 2 | 0 | 1 | 1  | 0 |

| Output  | 1 | 1 | 0  | 0 |

|         |   | O | R |   |

|---------|---|---|---|---|

| Input 1 | 1 | 0 | 1 | 0 |

| Input 2 | 0 | 1 | 1 | 0 |

| Output  | 1 | 1 | 1 | 0 |

|         |   | <b>NAND</b> |   |   |  |

|---------|---|-------------|---|---|--|

| Input 1 | 1 | 0           | 1 | 0 |  |

| Input 2 | 0 | 1           | 1 | 0 |  |

| Output  | 1 | 1           | 0 | 1 |  |

|         |   | XNOR |   |   |  |

|---------|---|------|---|---|--|

| Input 1 | 0 | 1    | 0 | 1 |  |

| Input 2 | 1 | 0    | 0 | 1 |  |

| Output  | 0 | 0    | 1 | 1 |  |

|         |   | Αľ | ND |   |

|---------|---|----|----|---|

| Input 1 | 0 | 1  | 0  | 1 |

| Input 2 | 1 | 0  | 0  | 1 |

| Output  | 0 | 0  | 0  | 1 |

|         |   | NOR |   |   |  |

|---------|---|-----|---|---|--|

| Input 1 | 0 | 1   | 0 | 1 |  |

| Input 2 | 1 | 0   | 0 | 1 |  |

| Output  | 0 | 0   | 1 | 0 |  |

### **LOGIC GATES**

The six logic gates paired according to their mirror opposite inputs and outputs. The pairings have been transformed in accordance with the symmetry constraints of Order 4.

Although the logic gates appear to operate based on assigning the absolute meanings of true and false for 1 and 0, the meanings are relational. The relationship is inherent in the symmetry of Order 4. A mirror exchanges 1 and 0, but not their relational meanings.

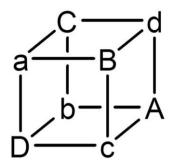

To see this, look at this drawing.

## **ORDER 4**

Two interpenetrating enantiomers of a chiral tetrahedron:

(a, b, c and d) and (A, B, C, D).

Now code each face of the cube by keeping the letters in alphabetical order, but writing 0 for a lower case letter (x: a, b, c or d) and 1 for an upper case letter (X: A, B, C or D). This constructs a table containing interpenetrating truth tables for XOR and XNOR.

| a, A | b, B | c, C | d, D |

|------|------|------|------|

| 0    | 1    | 1    | 0    |

| 0    | 1    | 0    | 1    |

| 1    | 1    | 0    | 0    |

| 1    | 0    | 0    | 1    |

| 1    | 0    | 1    | 0    |

| 0    | 0    | 1    | 1    |

# ORDER 4 The six different ways of ordering four distinct objects is controlled by interpenetrating truth tables for XOR and XNOR.

Any two adjacent rows form the input pairings for XOR in one direction and XNOR (inverting the outputs) in the other.

Look closely and you can also see how Order 4 braids the mutually exclusive ways of drawing distinctions under XOR and XNOR in the other four logic gates.

|         |   | X | OR |   |         |   | O | R       |   |

|---------|---|---|----|---|---------|---|---|---------|---|

| Input 1 | 1 | 0 | 1  | 0 | Input 1 | 1 | 0 | 1       | 0 |

| Input 2 | 0 | 1 | 1  | 0 | Input 2 | 0 | 1 | 1       | 0 |

| Output  | 1 | 4 | _  | _ | Output  | 4 | 1 | •       | 0 |

| •       | 1 | 1 | 0  | 0 | Output  | 1 | 1 | -       | 0 |

| • 203   | 1 |   | OR |   | Output  | 1 |   | ND      | U |

| Input 1 | 0 |   |    |   | Input 1 | 0 |   | ND<br>0 | 1 |

|         |   |   | OR |   |         |   |   |         |   |

### **LOGIC GATES**

The mirror paired logic gates showing the braiding of XOR and XNOR in AND, OR, NAND and NOR. The braiding is controlled by Order 4 symmetry.

The six logic gates transform in accordance with Order 4.

ORDER 4 and the Logic Gates

The six logic gates and the not operation are

constituted in the symmetry Order 4

## **Summary**

An object (x) is defined by a relationship formed by drawing a distinction between what it is (x) and what it is not (X). This relationship can be reformed by erasing the distinction (x,X) and drawing a new distinction (y,Y). Four distinct objects, a, b, c and d are each defined by a relationship between what each is (x) and is not (X): (a,A, b,B, c,C and d,D). This applies to the four different input pairings for a logic gate: 01, 10, 11 and 00. Symmetry constraints imposed by the six possible ways in which these four different objects can be reordered restricts what can happen when distinctions are reformed. The system will always transform such that there are three pairs of relational objects in a ring and one other relational object that separates the two sides of the relational objects (XOR from XNOR, AND from OR and NAND from NOR). Out of this emerge the six logic gates XOR, XNOR, OR, AND, NOR

and NAND, from which meaning emerges (same, different, etc.,) and also the NOT function, which separates each logic gate from its mirror pair.